# LP55271

# Tiny LED Driver for Camera Flash and 4 LEDs with I<sup>2</sup>C Programmability, Connectivity Test and Audio Synchronization

# **General Description**

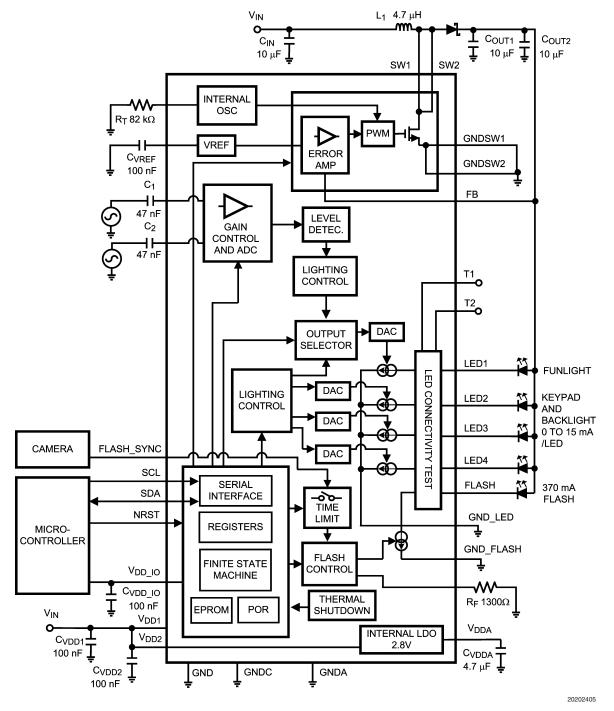

The LP55271 is a lighting management unit for handheld devices with I<sup>2</sup>C compatible control interface. The LP55271 has a step-up DC/DC converter with high current output and it drives display and keypad backlights and powers the camera flash LED. In addition the DC/DC converter has the output current to power for example an audio amplifier simultaneously. The chip has four 8-bit programmable high efficiency constant current LED drivers and a FLASH LED driver. Built-in audio synchronization feature allows the user to synchronize one of the LEDs to audio input.

The LP55271 has an integrated 370 mA flash driver with a safety stop feature and 46 mA torch mode. An external enable pin is provided for the synchronizing the flash with the camera action. An external software independent test interface provides a fast way to find a broken path or short on LED circuits. Very small microSMD package together with minimum number of external components is a best fit for handheld devices.

# **Features**

- High current boost DC-DC converter (up to 1A output current)

- Programmable boost output voltage

- 370 mA flash LED constant current driver with low tolerance and a safety circuit

- Synchronization pin for the flash timing

- Two single-ended audio inputs with gain control

- Four constant current 15 mA LED drivers with 8-bit programmable brightness control

- Audio synchronization feature

- I<sup>2</sup>C compatible control interface

- Built-in LED connectivity test to maximize manufacturing yield

- Small microSMD-30 package (2.5 mm x 3.0 mm x 0.6 mm)

# **Applications**

Camera FLASH, funlight and backlight driving in battery powered devices

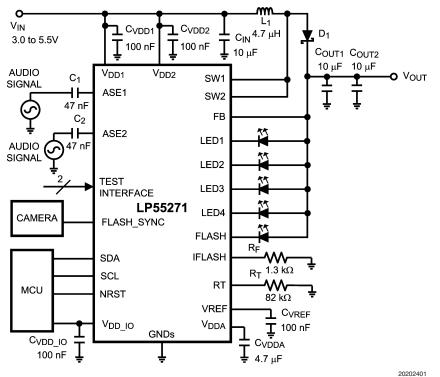

# **Typical Application**

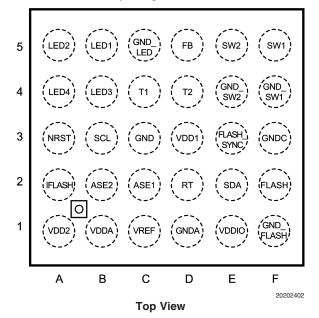

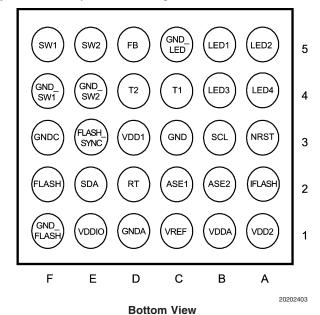

# **Connection Diagrams and Package Mark Information**

# **CONNECTION DIAGRAMS**

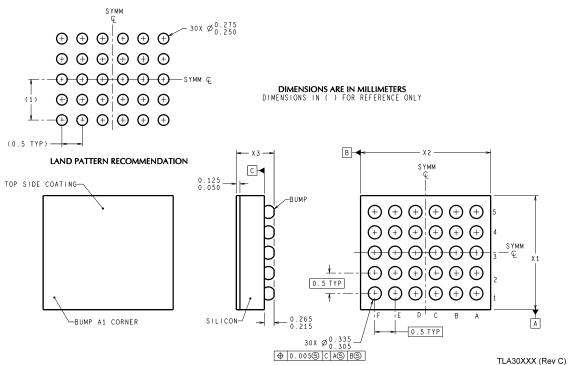

microSMD-30 package, 2.466 x 2.974 x 0.60 mm body size, 0.5 mm pitch NS Package Number TLA3011A

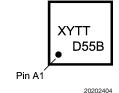

### **PACKAGE MARK**

Top View

XY—Date Code

TT—Die Traceability

D55B—Product Identification

# **ORDERING INFORMATION**

| Order Number | Package Marking | Supplied As | Spec/Flow |

|--------------|-----------------|-------------|-----------|

| LP55271TL    | D55B            | TNR 250     | NoPB      |

| LP55271TLX   | D55B            | TNR 3000    | NoPB      |

# **Connection Diagrams and Package Mark Information** (Continued) **Pin Descriptions**

| Pin | Name       | Туре | Description                                        |

|-----|------------|------|----------------------------------------------------|

| D3  | VDD1       | Р    | Supply Voltage                                     |

| A1  | VDD2       | Р    | Supply Voltage                                     |

| F5  | SW1        | Α    | Boost Converter Switch                             |

| E5  | SW2        | Α    | Boost Converter Switch                             |

| D5  | FB         | Α    | Boost Converter Feedback                           |

| B5  | LED1       | 0    | LED1 Driver Output                                 |

| A5  | LED2       | 0    | LED2 Driver Output                                 |

| B4  | LED3       | 0    | LED3 Driver Output                                 |

| A4  | LED4       | 0    | LED4 Driver Output                                 |

| F2  | FLASH      | 0    | Flash LED Driver Output                            |

| F3  | GNDC       | G    | Ground for Core Circuitry                          |

| D2  | RT         | Α    | Oscillator Frequency Setting                       |

| C1  | VREF       | Α    | Reference Voltage                                  |

| B1  | VDDA       | Р    | Internal LDO                                       |

| F4  | GND_SW1    | G    | Boost Converter Ground                             |

| E4  | GND_SW2    | G    | Boost Converter Ground                             |

| C5  | GND_LED    | G    | LEDs 1 to 4 Driver Ground Connection               |

| F1  | GND_FLASH  | G    | Flash Driver Ground Connection                     |

| A2  | IFLASH     | Α    | Resistor for Flash Current Setting                 |

| D1  | GNDA       | G    | Analog Ground Connection                           |

| C3  | GND        | G    | Ground                                             |

| E1  | VDD_IO     | Р    | Supply Voltage for Digital Interface               |

| A3  | NRST       | DI   | Low Active Reset                                   |

| В3  | SCL        | DI   | I <sup>2</sup> C Compatible Interface Clock Signal |

| E2  | SDA        | OD   | I <sup>2</sup> C Compatible Interface Data Signal  |

| E3  | FLASH_SYNC | DI   | FLASH LED Control                                  |

| D4  | T2         | DO   | Test Pin (Result)                                  |

| C4  | T1         | DI   | Test Pin (Clock)                                   |

| C2  | ASE1       | Al   | Audio Input                                        |

| B2  | ASE2       | Al   | Audio Input                                        |

A: Analog Pin D: Digital Pin G: Ground Pin P: Power Pin

I: Input Pin I/O: Input/Output Pin O: Output Pin OD: Open Drain Pin

# Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to +6.0V Voltage on power pins (V<sub>DD1.2</sub>) Voltage on analog pins -0.3V to V<sub>DD1.2</sub>+0.3V

with 6.0V max

Voltage on input/output pins -0.3V to  $V_{DD1.2}+0.3V$

with 6.0V max

Internally Limited

125°C

260°C

V(all other pins): Voltage to GND -0.3V to 6.0V I(V<sub>BEF</sub>) 10 µA I(FLASH) 500 mA

(Note 3)

Junction Temperature (T<sub>J-MAX</sub>)

Continuous Power Dissipation

-65°C to +150°C Storage Temperature Range

Maximum Lead Temperature (Reflow soldering, 3 times)

(Note 4)

ESD Rating (Note 5) Human Body Model

2 kV

# Operating Ratings (Note 1), (Note 2)

Voltage on power pins (V<sub>DD1.2</sub>) 3.0 to 5.5V Voltage on ASE1, ASE2 0V to 1.6V 1.65V to V<sub>DD1</sub>  $V_{DD\ IO}$ Junction Temperature (T<sub>J</sub>) Range -30°C to +125°C -30°C to +85°C Ambient Temperature (T<sub>A</sub>) Range (Note 6)

# **Thermal Properties**

Junction-to-Ambient Thermal 60 - 100°C/W

Resistance  $(\theta_{JA})$ ,

TLA3011A Package (Note 7)

# Electrical Characteristics (Notes 2, 8)

Limits in standard typeface are for T<sub>J</sub> = 25°C. Limits in boldface type apply over the operating ambient temperature range  $(-30^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C})$ . Unless otherwise noted, specifications apply to the LP55271 Block Diagram with:  $V_{\text{IN}} = 3.6\text{V}$ ,  $C_{\text{IN}} = 3.6\text{V}$ ,  $C_{\text{IN}}$ 10  $\mu$ F,  $C_{OUT1}$  = 10  $\mu$ F,  $C_{OUT2}$  = 10  $\mu$ F,  $C_{VDD\ IO}$  = 100 nF,  $C_{VREF}$  = 100 nF,  $C_{VDDA}$  = 4.7  $\mu$ F,  $C_{VDD1}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD3}$  = 100 nF,  $C_{VDD4}$  = 100 nF,  $C_{VDD5}$  = 100 nF,  $C_{VDD5}$  = 100 nF,  $C_{VDD5}$  = 100 nF,  $C_{VD5}$  = 100 nF,  $L_1 = 4.7 \mu H$ . (Note 9)

| Symbol                 | Parameter                                 | Condition                                 | Min | Тур  | Max | Units |

|------------------------|-------------------------------------------|-------------------------------------------|-----|------|-----|-------|

| I <sub>SHUT DOWN</sub> | Current of $V_{DD1} + V_{DD2}$ pins +     | Voltage on $V_{DD_{LO}} = 0V$ , NRST = L, |     | 1    | 5   | μΑ    |

|                        | Leakage Current of SW1, SW2,              | NSTBY(bit) = L                            |     |      |     |       |

|                        | LED1 to 4 and FLASH                       |                                           |     |      |     |       |

| I <sub>DD</sub>        | Active Mode Supply Current                | NRST = H, NSTBY(bit) = H, no load,        |     | 350  |     | μΑ    |

|                        | $(V_{DD1} + V_{DD2} current)$             | EN_BOOST(bit) = L, SCL, SDA = H           |     |      |     |       |

| I <sub>DD</sub>        | No load supply current                    | NSTBY(bit) = H, EN_BOOST(bit) = H,        |     | 850  |     | μΑ    |

|                        | $(V_{DD1} + V_{DD2} current)$             | SCL, SDA, NRST = H,                       |     |      |     |       |

|                        |                                           | AUTOLOAD_EN(bit) = L                      |     |      |     |       |

| I <sub>VDDIO</sub>     | V <sub>DD_IO</sub> Standby Supply current | NSTBY(bit) = L                            |     |      | 1   | μΑ    |

| $V_{DDA}$              |                                           | I <sub>VDDA</sub> = 1 mA                  | -4% | 2,8V | +4% | V     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables

Note 2: All voltages are with respect to the potential at the GND pins.

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>.I</sub> = 160°C (typ.) and disengages at T<sub>.I</sub> = 140°C (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note AN1112: Micro SMD Wafer Level Chip Scale

Note 5: The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. MIL-STD-883 3015.7

Note 6: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ . dissipation of the device in the application ( $P_{D\text{-}MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Note 8: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

Note 9: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

# LP55271 Block Diagram

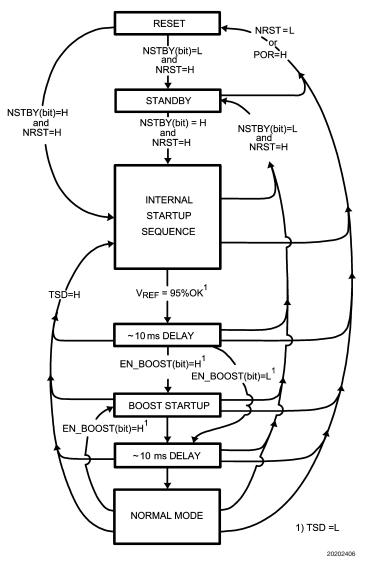

# **Modes of Operation**

**RESET:** In the reset mode all the internal registers are reset to the default values. Reset is entered always if input

NRST is LOW or internal Power On Reset (POR) is active. Power on reset will activate during the chip startup or when the supply voltage  $V_{DD2}$  falls below 1.5V. Once  $V_{DD2}$  rises above 1.5V, POR will inactivate and the chip will continue to the STANDBY mode. NSTBY control bit is low after POR by default.

STANDBY: The standby mode is entered if the register bit NSTBY is LOW and reset is not active. This is the low power

consumption mode, when all circuit functions are disabled. Registers can be written in this mode and the

control bits are effective immediately after start up.

STARTUP: When NSTBY bit is written high, the internal startup sequence powers up all the needed internal blocks

$(V_{\mathsf{REF}},$  Oscillator, etc.). To ensure the correct oscillator initialization, a 10 ms delay is generated by the internal state-machine. If the chip temperature rises too high, the thermal shutdown (TSD) disables the chip

operation and startup mode is entered until no thermal shutdown event is present.

**BOOST STARTUP:** Soft-start for boost output is generated in the boost startup mode. The boost output is raised in a low current

PWM mode during the 10 ms delay generated by the state-machine. The boost startup is entered from internal startup sequence if EN\_BOOST is HIGH or from normal mode when EN\_BOOST is written HIGH.

NORMAL: During normal mode the user controls the chip using the Control Registers. The registers can be written in

any sequence and any number of bits can be altered in a register in one write.

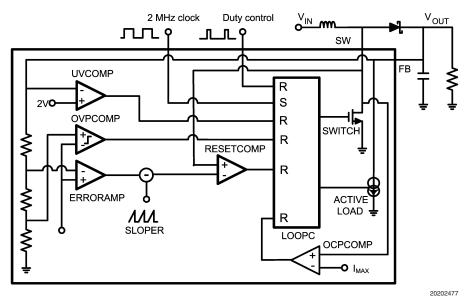

# Magnetic Boost DC/DC Converter

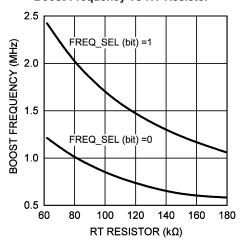

The LP55271 boost DC/DC converter generates a 4.00 - 5.40V output voltage to drive the LEDs from a single Li-lon battery (3.0V to 4.5V). The output voltage is controlled with a 4-bit register in 8 steps. The converter is a magnetic switching PWM mode DC/DC converter with a current limit. The converter has 2.0 MHz / 1.0 MHz selectable switching frequency operation, when the timing resistor RT is 82  $\rm k\Omega$ .

The LP55271 boost converter uses pulse-skipping elimination method to stabilize the noise spectrum. Even with light load or no load a minimum length current pulse is fed to the inductor. An internal active load is used to remove the excess charge from the output capacitor when needed.

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the inductor current is measured and controlled with the feedback. The output voltage control changes the resistor divider in the feedback loop.

The following figure shows the boost topology with the protection circuitry. Four different protection schemes are implemented:

- Over voltage protection, limits the maximum output voltage.

- Keeps the output below breakdown voltage.

- Prevents boost operation if battery voltage is much higher than desired output.

- Over current protection, limits the maximum inductor current.

- Voltage over switching NMOS is monitored; too high voltages turn the switch off.

- 3. Feedback (FB) protection for no connection.

- 4. Duty cycle limiting, done with digital control.

**Boost Converter Topology**

7

20202411

# Magnetic Boost DC/DC Converter (Continued)

### MAGNETIC BOOST DC/DC CONVERTER ELECTRICAL CHARACTERISTICS

Limits in standard typeface are for  $T_J$  = 25°C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A$  < +85°C). Unless otherwise noted, specifications apply to the LP55271 Block Diagram with:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT1}$  = 10  $\mu$ F,  $C_{OUT2}$  = 10  $\mu$ F,  $C_{VDDIO}$  = 100 nF,  $C_{VREF}$  = 100 nF,  $C_{VDDA}$  = 4.7  $\mu$ F,  $C_{VDD1}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD3}$  = 100 nF,  $C_{VD3}$  =

| Symbol               | Parameter                  | Conditions                                                  | Min | Тур                                     | Max | Units |

|----------------------|----------------------------|-------------------------------------------------------------|-----|-----------------------------------------|-----|-------|

| I <sub>LOAD</sub>    | Load Current               | $3.2V \le V_{IN} \le 4.5V$                                  |     |                                         | 670 | mA    |

|                      | (Note 10)                  | $V_{OUT} = 5.0V$                                            |     |                                         |     |       |

| V <sub>OUT</sub>     | Output Voltage Accuracy    | $3.2V \le V_{IN} \le 4.5V$                                  | -5  |                                         | +5  | %     |

|                      | (FB pin)                   | V <sub>OUT</sub> (target value) = 5.0V, active load off     |     |                                         |     |       |

|                      | Output Voltage<br>(FB Pin) | $3.0V \le V_{IN} \le (5.0V + V_{SCHOTTKY})$ active load off |     | 5.0                                     |     | V     |

|                      |                            | $V_{IN} > (5.0V + V_{SCHOTTKY})$                            |     | V <sub>IN</sub> - V <sub>SCHOTTKY</sub> |     |       |

| RDS <sub>ON</sub>    | Switch ON Resistance       | $V_{IN} = 3.6V, I_{SW} = 1.0A$                              |     | 0.20                                    | 0.4 | Ω     |

| f <sub>PWF</sub>     | PWM Mode Switching         | RT = 82 kΩ                                                  |     |                                         |     | MHz   |

|                      | Frequency                  | FREQ_SEL (bit) = 1                                          |     | 2.0                                     |     |       |

|                      |                            | FREQ_SEL (bit) = 0                                          |     | 1.0                                     |     |       |

|                      | Frequency Accuracy         | $3.2V \le V_{DD1,2} \le 5.0V$                               | -6  | ±3                                      | +6  | %     |

|                      |                            | $RT = 82 \text{ k}\Omega$                                   | -9  |                                         | +9  |       |

| t <sub>PULSE</sub>   | Switch Pulse Minimum       | no load                                                     |     | 25                                      |     | ns    |

|                      | Width                      |                                                             |     |                                         |     |       |

| t <sub>STARTUP</sub> | Startup Time               |                                                             |     | 10                                      |     | ms    |

| I <sub>CL_OUT</sub>  | SW1 + SW2 current limit    |                                                             |     | 1.7                                     |     | А     |

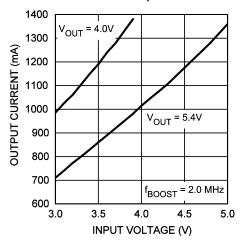

Note 10: Specified currents are the worst case currents. If input voltage is larger or output voltage is smaller, current can be increased according to graph "Boost Maximum Output Current".

# **BOOST STANDBY MODE**

User can set the boost converter to STANDBY mode by writing the register bit EN\_BOOST low when there is no load to avoid idle current consumption. When EN\_BOOST is written high, the converter starts in low current PWM (Pulse Width Modulation) mode for 10 ms and then goes to normal PWM mode.

| FREQ_SEL Bit | Boost Switching<br>Frequency<br>(Typical) |

|--------------|-------------------------------------------|

| 0            | 1.0 MHz default                           |

| 1            | 2.0 MHz                                   |

## **BOOST CONTROL REGISTERS**

User can control the boost output voltage and the switching frequency according to the following tables.

| Boost Output Voltage<br>[3:0] Register | Boost Output Voltage (V)<br>(Typical) |

|----------------------------------------|---------------------------------------|

| 0000                                   | 4.00                                  |

| 0001                                   | 4.20                                  |

| 0011                                   | 4.40                                  |

| 0111                                   | 4.60 default                          |

| 1000                                   | 4.80                                  |

| 1001                                   | 5.00                                  |

| 1011                                   | 5.20                                  |

| 1111                                   | 5.40                                  |

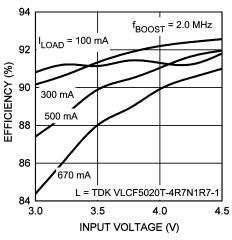

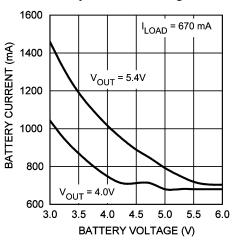

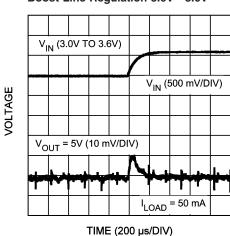

# **Boost Converter Typical Performance Characteristics**

$T_J$  = 25°C. Unless otherwise noted, typical performance characteristics apply to the LP55271 Block Diagram with:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 5.0V,  $C_{IN}$  = 10  $\mu\text{F},~C_{OUT_1}$  = 10  $\mu\text{F},~C_{OUT_2}$  = 10  $\mu\text{F},~C_{VDD\_IO}$  = 100 nF,  $C_{VREF}$  = 100 nF,  $C_{VDDA}$  = 4.7  $\mu\text{F},~C_{VDD_1}$  = 100 nF,  $C_{VDD_2}$  = 100 nF, L1 = 4.7  $\mu\text{H}$  (Note 9).

### **Boost Converter Efficiency**

20202479

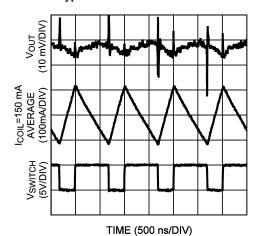

### Boost Typical Waveforms at 100 mA Load

20202480

### **Battery Current vs Voltage**

20202481

### **Boost Frequency vs RT Resistor**

20202482

## Boost Line Regulation 3.0V - 3.6V

20202483

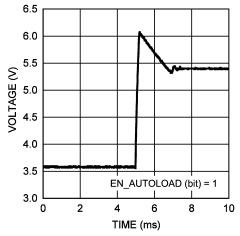

### Boost Startup to 5.4V with no Load

20202484

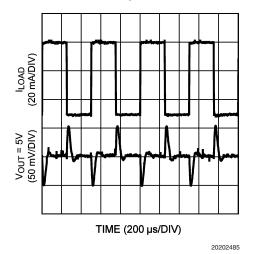

# **Boost Converter Typical Performance Characteristics** (Continued)

Boost Load Transient Response, 50 mA to 100 mA

# **Boost Maximum Output Current**

20202498

# Flash Driver

LP55271 has an internal constant current driver that is capable for sinking low (46 mA) and high (370 mA) current mainly targeted for torch and flash LED in camera phone applications. 370 mA flash driver can be hardware or software enabled. Flash safety function prevents hardware damages due to possible overheating when the flash has been stuck on because of a hardware, software or user error.

Flash safety counter starts counting when the flash is activated and disables the flash automatically when the pre-

defined 1.0s or 2.0s time limit is reached. Flash is activated with FLASH\_SYNC bit or FLASH\_SYNC pin, as defined in the table below. Safety time limit is defined by SAFETY\_TIME bit. (Time limit is 2.0s if SAFETY\_TIME bit is low and 1.0s if the bit is high.)

Flash driver currents — both torch and flash — are set with external resistor R  $_{\rm F}$ . The flash current is 480/R $_{\rm F}$  amperes and the torch current is 60/R $_{\rm F}$  amperes. User should not use lower resistance value than 1200 $\Omega$ .

### Flash LED Control (X = don't care)

| EN_TORCH bit | EN_FLASH bit | FLASH_SYNC bit or pin       | SAFETY_TIME bit    | Flash LED Action |

|--------------|--------------|-----------------------------|--------------------|------------------|

| 0            | 0            | X                           | X                  | Off              |

| 1            | 0            | X                           | X                  | Torch            |

| X            | 1            | Change from LOW to HIGH to  | 0 for 2.0 seconds; | Flash            |

|              |              | engage; from HIGH to LOW to | 1 for 1.0 second   |                  |

|              |              | disengage                   |                    |                  |

### Flash Programming Example

| Address | Data | Function                                                                                            |

|---------|------|-----------------------------------------------------------------------------------------------------|

| 00H     | 8FH  | Sets safety time to 1.0s. In this example LED1 to LED4 are enabled.                                 |

| 00H     | 9FH  | Enables torch.                                                                                      |

| 00H     | FFH  | Activates FLASH. EN_FLASH bit and FLASH_SYNC bit are written simultaneously because EN_FLASH        |

|         |      | disables torch.                                                                                     |

| 00H     | BFH  | Disables FLASH. If FLASH is disabled by safety time, FLASH_SYNC bit needs to be written to 0 before |

|         |      | next FLASH.                                                                                         |

### FLASH DRIVER ELECTRICAL CHARACTERISTICS

Limits in standard typeface are for  $T_J$  = 25°C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A$  < +85 °C). Unless otherwise noted, specifications apply to the LP55271 Block Diagram with:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT1}$  = 10  $\mu$ F,  $C_{OUT2}$  = 10  $\mu$ F,  $C_{VDDIO}$  = 100 nF,  $C_{VDDA}$  = 4.7  $\mu$ F,  $C_{VDD1}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VD2}$  = 100 nF,

| Symbol               | Parameter                    | Condition                    | Min  | Тур | Max  | Units |

|----------------------|------------------------------|------------------------------|------|-----|------|-------|

| I <sub>FLASH</sub>   | Flash Mode Sink Current      | $3.0V \le V_{IN} \le 5.5V$ , |      | 370 |      | mA    |

|                      | (Note 8)                     | V <sub>FLASH</sub> = 1.0V    | -7.5 |     | +7.5 | %     |

| I <sub>TORCH</sub>   | Torch Mode Sink Current      | $3.0V \le V_{IN} \le 5.5V$   |      | 46  |      | mA    |

|                      | (Note 8)                     |                              |      |     |      |       |

| I <sub>LEAKAGE</sub> | Flash Driver Leakage Current | V <sub>FB</sub> = 5.0V       |      | 0.1 |      | μA    |

| t <sub>FLASH</sub>   | Flash Turn-On Time           |                              |      | 20  |      | μs    |

|                      | (Note 11)                    |                              |      |     |      |       |

| V <sub>SAT</sub>     | Saturation Voltage           | $3.0V \le V_{IN} \le 5.5V$ , |      | 550 |      | mV    |

|                      |                              | Current Decreased to 95% of  |      |     |      |       |

|                      |                              | the Maximum Sink Current     |      |     |      |       |

| t <sub>SAFETY</sub>  | Safety Time Accuracy         |                              | -9   |     | +9   | %     |

Note 11: Flash turn-on time is measured from the moment the flash is activated until the flash current crosses 90% of its target value.

# Constant Current Sink Outputs LED1, LED2, LED3, LED4

LP55271 has four independent backlight/keypad LED drivers. All the drivers are regulated constant current sinks. LED currents are controlled by 8-bit current mode DACs. Every driver can be controlled in two ways:

- 1. Brightness control with constant current drivers

- Direct ON/OFF control. The current is pre-set by 8-bit current mode DAC.

In addition, LED1 driver can be synchronized to audio input signal amplitude.

By using brightness control user can set brightness of every single LED by using 8-bit brightness control registers. If analog audio is available on system the user can use audio synchronization for synchronizing LED1 to the music. Direct ON/OFF control is mainly for switching LEDs on and off.

LED Control Register (00 hex) has control bits for direct on/off control of all the LEDs. Note that the LEDs have to be turned on in order to control them with audio synchronization (LED1 only) or brightness control.

The brightness is programmed as described in the following.

$I_{LED} = n x (15 \text{ mA} / 255)$

where:

n = LED[7:0] (8-bit)

step = 15 mA / 255  $\approx$  0.05882 mA

For example if 13.2 mA is required for driver current:

$n = 13.2 \text{ mA} / (15 \text{ mA} / 255) \approx 224$

224 = 1110 0000, E0 hex

### **LED1 to LED4 Brightness Control**

| LED1[7:0], LED2[7:0], LED3[7:0] and LED4[7:0] Registers | Driver Current, mA (typical) |

|---------------------------------------------------------|------------------------------|

| 0000 0000                                               | 0                            |

| 0000 0001                                               | 0.059                        |

| 0000 0010                                               | 0.118                        |

| •                                                       | •                            |

| 1110 0000                                               | 13.176                       |

| •                                                       | •                            |

| 1111 1110                                               | 14.941                       |

| 1111 1111                                               | 15                           |

### LED1 TO LED4 DRIVERS ELECTRICAL CHARACTERISTICS

Limits in standard typeface are for  $T_J = 25^{\circ}C$ . Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A < +85^{\circ}C$ ). Unless otherwise noted, specifications apply to the LP55271 Block Diagram with:  $V_{IN} = 3.6V$ ,  $C_{IN} = 10~\mu F$ ,  $C_{OUT1} = 10~\mu F$ ,  $C_{OUT2} = 10~\mu F$ ,  $C_{VDDIO} = 100~n F$ ,  $C_{VREF} = 100~n F$ ,  $C_{VDDA} = 4.7~\mu F$ ,  $C_{VDD1} = 100~n F$ ,  $C_{VDD2} = 100~n F$ ,  $C_{VDD2} = 100~n F$ ,  $C_{VDD2} = 100~n F$ ,  $C_{VDD3} = 100~n F$ ,  $C_{VD3} = 100~n F$ ,  $C_{VD$

| Symbol               | Parameter             | Condition                                  | Min | Тур  | Max | Units |

|----------------------|-----------------------|--------------------------------------------|-----|------|-----|-------|

| I <sub>MAX</sub>     | Maximum Sink Current  |                                            |     | 15   |     | mA    |

| I <sub>LEAKAGE</sub> | Leakage Current       | $V_{FB} = 5.0V$                            |     | 0.03 |     | μA    |

| I <sub>LED</sub>     | Current Tolerance     | I <sub>SINK</sub> = 13.2 mA (target value) |     | 13.2 |     | mA    |

|                      |                       |                                            | -7  |      | +7  | %     |

| I <sub>MATCH</sub>   | Sink Current Matching | I <sub>SINK</sub> = 13.2 mA                |     | 1    |     | %     |

|                      | Between LED 1 to 4    |                                            |     |      |     |       |

| $V_{SAT}$            | Saturation Voltage    | $3.0V \le V_{IN} \le 5.5V,$                |     | 150  | 230 | mV    |

|                      |                       | Current Decreased to 95% of the            |     |      |     |       |

|                      |                       | Maximum Sink Current                       |     |      |     |       |

Note: Sink current matching is the maximum difference from the average.

# **Audio Synchronization**

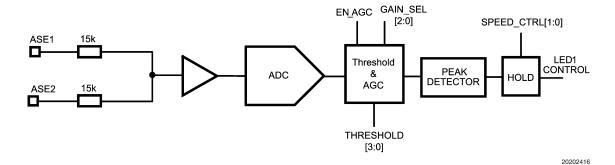

The LED1 output can be synchronized to incoming audio signal with Audio Synchronization feature. Audio Synchronization synchronizes LED1 based on input signal's peak amplitude. Programmable gain and automatic gain control function are also available for adjustment of input signal amplitude to light response. Control of LED1 brightness refreshing frequency is done with four different frequency configurations. The digitized input signal has a DC component that is removed by a digital DC-remover. The DC-remover is a high-pass filter where corner frequency is user selectable by using DC\_FREQ bit. LP55271 has 2-channel audio (stereo) input for audio synchronization, as shown in the figure below. The inputs accept signals in the range of 0V to 1.6V peak-to-peak and these signals are mixed into a single wave so that they can be filtered simultaneously.

LP55271 audio synchronization is mainly done digitally and it consists following signal path blocks (see figure below).

- Input buffer

- · AD converter

- Automatic Gain Control (AGC) and manually programmable gain

- · Peak detector

Automatic Gain Control (AGC) adjusts the input signal to suitable range automatically. User can disable AGC and the gain can be set manually with programmable gain. Audio synchronization is based on peak detection method.

### **Audio Synchronization Input Electrical Parameters**

| Symbol          | Parameter          | Conditions                          | Min | Тур | Max  | Units |

|-----------------|--------------------|-------------------------------------|-----|-----|------|-------|

| Z <sub>IN</sub> | Input Impedance of |                                     | 10  | 15  |      | kΩ    |

|                 | ASE1, ASE2         |                                     |     |     |      |       |

| A <sub>IN</sub> | ASE1, ASE2 Audio   | Min input level needs maximum gain; | 0   |     | 1600 | mV    |

|                 | Input Level Range  | Max input level for minimum gain.   |     |     |      |       |

|                 | (peak-to-peak)     |                                     |     |     |      |       |

### **CONTROL OF AUDIO SYNCHRONIZATION**

The following table describes the controls required for audio synchronization. LED1 brightness control through serial interface is not available when audio synchronization is enabled.

### **Audio Synchronization Control**

| EN_SYNC         | Audio synchronization enabled. Set EN_SYNC = 1 to enable audio synchronization or 0 to disable. |  |  |

|-----------------|-------------------------------------------------------------------------------------------------|--|--|

| EN_AGC          | Automatic gain control. Set EN_AGC = 1 to enable automatic control or 0 to disable.             |  |  |

|                 | When EN_AGC is disabled, the audio input signal gain value is defined by GAIN_SEL.              |  |  |

| GAIN_SEL[2:0]   | Input signal gain control. Gain has a range from 0 dB to -46 dB.                                |  |  |

| SPEED_CTRL[1:0] | Control for refreshing frequency. Sets the typical refreshing rate for the LED1 output.         |  |  |

| THRESHOLD[3:0]  | Control for the audio input threshold. Sets the typical threshold for the audio inputs signals. |  |  |

|                 | May be needed if there is noise on the audio lines.                                             |  |  |

| DC_FREQ         | Control for the high-pass filter corner frequency.                                              |  |  |

|                 | 0 = 80 Hz                                                                                       |  |  |

|                 | 1 = 510 Hz                                                                                      |  |  |

# Audio Synchronization (Continued)

### **Audio Input Threshold Setting**

| Threshold[3:0] | Threshold Level, mV (typical) |  |

|----------------|-------------------------------|--|

| 0000           | Disabled                      |  |

| 0001           | 0.2                           |  |

| 0010           | 0.4                           |  |

| *              | *                             |  |

| *              | *                             |  |

| 1110           | 2.5                           |  |

| 1111           | 2.7                           |  |

|                |                               |  |

# Typical Gain Values vs. Audio Input Amplitude

| Audio Input Amplitude mV <sub>P-P</sub> | Gain Value dB |

|-----------------------------------------|---------------|

| 0 to 10                                 | 0             |

| 0 to 20                                 | -6            |

| 0 to 40                                 | -12           |

| 1 to 85                                 | -18           |

| 3 to 170                                | -24           |

| 5 to 400                                | -31           |

| 10 to 800                               | -37           |

| 20 to 1600                              | -46           |

# **Input Signal Gain Control**

| GAIN_SEL[2:0] | Gain dB |

|---------------|---------|

| 000           | 0       |

| 001           | -6      |

| 010           | -12     |

| 011           | -18     |

| 100           | -24     |

| 101           | -31     |

| 110           | -37     |

| 111           | -46     |

# Refreshing Frequency

| SPEED_CTRL[1:0] | Refreshing Rate Hz |

|-----------------|--------------------|

| 00              | FASTEST            |

| 01              | 15                 |

| 10              | 7.6                |

| 11              | 3.8                |

# **Logic Interface Characteristics**

Limits in standard typeface are for  $T_J$  = 25°C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A$  < +85°C). Unless otherwise noted, specifications apply to the LP55271 Block Diagram with:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT1}$  = 10  $\mu$ F,  $C_{OUT2}$  = 10  $\mu$ F,  $C_{VDDIO}$  = 100 nF,  $C_{VREF}$  = 100 nF,  $C_{VDDA}$  = 4.7  $\mu$ F,  $C_{VDD1}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD2}$  = 100 nF,  $C_{VDD3}$  = 100 nF,  $C_{VDD4}$  = 100 nF,  $C_{VDD4}$  = 100 nF,  $C_{VDD5}$  = 100 nF,  $C_{VD5}$  = 100 nF,

| Symbol            | Parameter                       | Condition                                            | Min                      | Typical | Max                      | Unit |  |  |

|-------------------|---------------------------------|------------------------------------------------------|--------------------------|---------|--------------------------|------|--|--|

| Logic Inp         | Logic Inputs SCL and FLASH_SYNC |                                                      |                          |         |                          |      |  |  |

| V <sub>IL</sub>   | Input Low Level                 | $V_{\rm DD\_IO}$ = 1.65V to $V_{\rm DD1,2}$          |                          |         | 0.2 x V <sub>DD_IO</sub> | V    |  |  |

| V <sub>IH</sub>   | Input High Level                |                                                      | 0.8 x V <sub>DD_IO</sub> |         |                          | V    |  |  |

| I <sub>I</sub>    | Input Current                   |                                                      | -1.0                     |         | 1.0                      | μΑ   |  |  |

| f <sub>SCL</sub>  | SCL Pin Clock Frequency         |                                                      |                          | 400     |                          | kHz  |  |  |

| Logic Inp         | out NRST                        |                                                      | ·                        |         |                          |      |  |  |

| V <sub>IL</sub>   | Input Low Level                 | $V_{\rm DD_{-}IO} = 1.65V \text{ to } V_{\rm DD1,2}$ |                          |         | 0.5                      | V    |  |  |

| V <sub>IH</sub>   | Input High Level                |                                                      | 1.2                      |         |                          | V    |  |  |

| I <sub>1</sub>    | Input Current                   |                                                      | -1.0                     |         | 1.0                      | μΑ   |  |  |

| t <sub>NRST</sub> | Reset Pulse Width               |                                                      | 10                       |         |                          | μs   |  |  |

| Logic Inp         | Logic Input/Output SDA          |                                                      |                          |         |                          |      |  |  |

| V <sub>OL</sub>   | Output Low Level                | I <sub>OUT</sub> = 3 mA                              |                          | 0.3     | 0.5                      | V    |  |  |

| IL                | Output leakage current          | V <sub>OUT</sub> = 2.8V                              |                          |         | 1.0                      | μΑ   |  |  |

# I<sup>2</sup>C Compatible Interface

### I<sup>2</sup>C SIGNALS

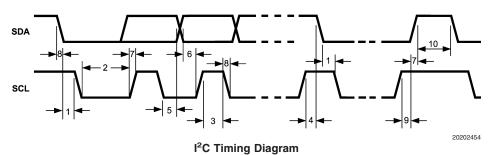

The SCL pin is used for the  $I^2C$  clock and the SDA pin is used for bidirectional data transfer. Both these signals need a pull-up resistor according to  $I^2C$  specification. The values of the pull-up resistors are determined by the capacitance of the bus (typ. ~1.8 k $\Omega$ ). Signal timing specifications are shown in table  $I^2C$  Timing Parameters.

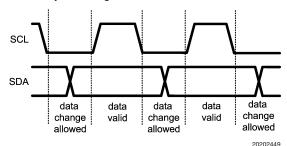

### I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

I<sup>2</sup>C Signals: Data Validity

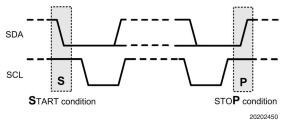

### I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

I<sup>2</sup>C Start and Stop Conditions

### TRANSFERRING DATA

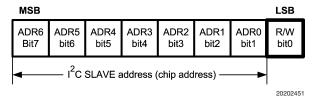

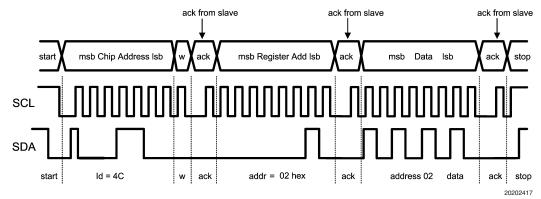

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9<sup>th</sup> clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LP55271 address is 4C hex. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

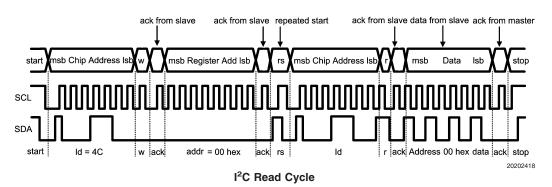

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the  $I^2C$  Read Cycle waveform.

I<sup>2</sup>C Chip Address 4C hex for LP55271

# I<sup>2</sup>C Compatible Interface (Continued)

w = write (SDA = "0")

r = read (SDA = "1")

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = chip address, 4C hex for LP55271.

## I<sup>2</sup>C Write Cycle

# I<sup>2</sup>C TIMING PARAMETERS ( $V_{DD1,2}$ = 3.0 to 4.5V, $V_{DDIO}$ = 1.65V to $V_{DD1,2}$ )

| Symbol | Parameter                                                     | Limit                |     | Units |  |

|--------|---------------------------------------------------------------|----------------------|-----|-------|--|

| Symbol | Parameter                                                     | Min                  | Max | Units |  |

| 1      | Hold Time (repeated) START Condition                          | 0.6                  |     | μs    |  |

| 2      | Clock Low Time                                                | 1.3                  |     | μs    |  |

| 3      | Clock High Time                                               | 600                  |     | ns    |  |

| 4      | Setup Time for a Repeated START Condition                     | 600                  |     | ns    |  |

| 5      | Data Hold Time (Output direction, delay generated by LP55271) | 300                  | 900 | ns    |  |

| 5      | Data Hold Time (Input direction)                              | 0                    | 900 | ns    |  |

| 6      | Data Setup Time                                               | 100                  |     | ns    |  |

| 7      | Rise Time of SDA and SCL                                      | 20+0.1C <sub>b</sub> | 300 | ns    |  |

| 8      | 8 Fall Time of SDA and SCL                                    |                      | 300 | ns    |  |

| 9      | Set-up Time for STOP condition                                | 600                  |     | ns    |  |

# I<sup>2</sup>C Compatible Interface (Continued)

| 10             | Bus Free Time between a STOP and a START Condition | 1.3 |     | μs |   |

|----------------|----------------------------------------------------|-----|-----|----|---|

| C <sub>b</sub> | Capacitive Load for Each Bus Line                  | 10  | 200 | pF | ĺ |

NOTE: Data guaranteed by design

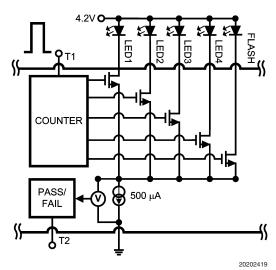

# **Test Interface**

The test bus can be controlled externally or internally. For the external control, the LP55271 pins  $V_{\rm DD1,2}$  only need to be powered. External control is independent on status of NRST and  $V_{\rm DDIO}$  pins. T1 is an input and it has an internal 6

$k\Omega$  pull-down resistor. T2 is an output line for the test result with an internal 200  $k\Omega$  pull-down resistor. When T1 is low, T2 is always pulled down; when T1 is high, T2 is indicating the result of the test.

High Level Schematic Representation of the Test Interface

The device is capable of detecting a defective unit in three cases:

- Production test 1: The LP55271 is assembled on a printed wiring board (PWB), but there is no LEDs connected on current sink outputs. An external 4.2V test voltage is supplied on the V<sub>DD1</sub> and V<sub>DD2</sub> pins, from which follows that the reset operating mode is entered with POR. Test pin T1 is pulled high. The chip will send an acknowledge "1" onto the T2 pin if the chip is in working order; otherwise T2 stays low (0). Refer to Test Interface Timing Diagram.

- Production test 2: The LP55271 is assembled on a PWB with the external components shown in LP55271 Block Diagram. 4.2V voltage is connected to V<sub>DD1</sub>, V<sub>DD2</sub> and FB pins (see the figure above), from which follows that the reset operating mode is entered with POR. Test pin T1 is pulled high. The chip will send an acknowledge

- "1" onto the T2 pin if the chip is in working order; otherwise T2 stays low (0). If the ACK is "1", a repetitive test pattern "0-1-0-1-0-1-0-1-0-1" is applied to T1 pin and if the LED corresponding the pattern (see Test Interface Timing Diagram) is connected properly T2 gives "1", otherwise T2 stays low. The last "1" disengages the test.

- Field test: Build-in self-test through the I<sup>2</sup>C compatible control interface. The LP55271 is enabled (NSTBY(bit) = 1, EN\_BOOST(bit) = 1) and external test pins T1 and T2 are disconnected. The result can be read through the I<sup>2</sup>C compatible control interface. LED test is enabled by writing to address 0Ch hex data 01h. Result can be read from the same address during the next I<sup>2</sup>C cycle. Note: I<sup>2</sup>C compatible interface clock signal controls the timing of the test procedure. For that reason the clock signal frequency should be 50 kHz or less during the build-in self-test.

# Test Interface (Continued)

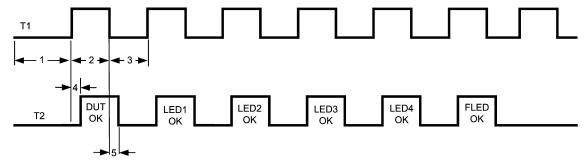

**Test Interface Timing Diagram**

20202420

# **Test Interface Timing Parameters**

|        |                    |                                            | Limit |     |       |

|--------|--------------------|--------------------------------------------|-------|-----|-------|

| Symbol | Condition          | Parameter                                  | Min   | Max | Units |

| 1      | $V_{DD1,2} = 4.2V$ | Setup Time after V <sub>DD1,2</sub> = 4.2V | 1     |     | ms    |

| 2      |                    | Clock High Time                            | 200   |     | μs    |

| 3      |                    | Clock Low Time                             | 200   |     | μs    |

| 4      |                    | Test Result Settling Time                  |       | 10  | μs    |

| 5      |                    | Data Hold Time                             | 0     | 10  | ns    |

NOTE: Data guaranteed by design

# **Test Interface Characteristics**

Limits in standard typeface are for  $T_J = 25^{\circ}C$ .

| Symbol             | Parameter                 | Condition                                                  | Min                      | Тур  | Max | Units |  |

|--------------------|---------------------------|------------------------------------------------------------|--------------------------|------|-----|-------|--|

| Logic Input        | Logic Input T1            |                                                            |                          |      |     |       |  |

| V <sub>IL</sub>    | Input Low Level           | $V_{DD1,2} = 4.2V$                                         |                          |      | 0.5 | V     |  |

| V <sub>IH</sub>    | Input High Level          |                                                            | 1.2                      |      |     | V     |  |

| Logic Outp         | ut T2                     |                                                            |                          |      |     |       |  |

| V <sub>OL</sub>    | Output Low Level          | $V_{DD1,2} = 4.2V$ , $I_{OUT} = 3$ mA (pull-up current)    |                          | 0.3  | 0.5 | V     |  |

| V <sub>OH</sub>    | Output High Level         | $V_{DD1,2} = 4.2V$ , $I_{OUT} = -3$ mA (pull-down current) | V <sub>DD1,2</sub> - 0,5 | 3.9  |     | V     |  |

| Internal Cu        | rrent Sink                |                                                            |                          |      |     |       |  |

| I <sub>SINK</sub>  | Sink Current              | $V_{DD1,2} = 4.2V$                                         |                          | 500  |     | μA    |  |

| Connectivit        | y Test Pass Range         |                                                            |                          |      |     |       |  |

| V <sub>PASS1</sub> | Voltage Over the Internal | Production test cases                                      |                          | 0.10 |     | V     |  |

|                    | Current Sink; Low Level   | $V_{DD1,2} = 4.2V$                                         | -50                      |      | +50 | %     |  |

| V <sub>PASS2</sub> | Voltage Over the Internal | $V_{OUT} = 3.9V \text{ to } 4.2V$                          |                          | 2.90 |     | V     |  |

|                    | Current Sink; High Level  |                                                            | -10                      |      | +10 | %     |  |

| V <sub>PASS3</sub> | Voltage Over the Internal | Field test cases                                           |                          | 0.40 |     | V     |  |

|                    | Current Sink; Low Level   | $V_{DD1,2} = 3.0V \text{ to } 4.2V$                        | -30                      |      | +30 | %     |  |

| V <sub>PASS4</sub> | Voltage Over the Internal | $V_{OUT} = 5.0V \pm 5\%$                                   |                          | 3.95 |     | V     |  |

|                    | Current Sink; High Level  |                                                            | -10                      |      | +10 | %     |  |

NOTE: Data guaranteed by design

# Recommended External Components

# OUTPUT CAPACITOR, COUT1, COUT2

The output capacitors  $C_{OUT1}$ ,  $C_{OUT2}$  directly affect the magnitude of the output ripple voltage. In general, the higher the value of  $C_{OUT}$ , the lower the output ripple magnitude. Multilayer ceramic capacitors with low ESR are the best choice. At the lighter loads, the low ESR ceramics offer a much lower  $V_{OUT}$  ripple that the higher ESR tantalums of the same value. At the higher loads, the ceramics offer a slightly lower  $V_{OUT}$  ripple magnitude than the tantalums of the same value. However, the dv/dt of the  $V_{OUT}$  ripple with the ceramics is much lower that the tantalums under all load conditions. Capacitor voltage rating must be sufficient, 10V is recommended

Some ceramic capacitors, especially those in small packages, exhibit a strong capacitance reduction with the increased applied voltage. The capacitance value can fall to below half of the nominal capacitance. Too low output capacitance can make the boost converter unstable.

# INPUT CAPACITOR, CIN

The input capacitor  $C_{\text{IN}}$  directly affects the magnitude of the input ripple voltage and to a lesser degree the  $V_{\text{OUT}}$  ripple. A higher value  $C_{\text{IN}}$  will give a lower  $V_{\text{IN}}$  ripple. Capacitor voltage rating must be sufficient, 10V or greater is recommended.

### OUTPUT DIODE, D<sub>1</sub>

The output diode for a boost converter must be chosen correctly depending on the output voltage and the output current. The diode must be rated for a reverse voltage

greater than the output voltage used. The average current rating must be greater than the maximum load current expected, and the peak current rating must be greater than the peak inductor current (~1.7A at maximum load). A Schottky diode should be used for the output diode. Schottky diodes with a low forward voltage drop (VF) and fast switching speeds are ideal for increasing efficiency in portable applications. Do not use ordinary rectifier diodes, since slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer. In Schottky barrier diodes reverse leakage current increases quickly with the junction temperature. Therefore, reverse power dissipation and the possibility of thermal runaway has to be considered when operating under high temperature conditions. Examples of suitable diodes are Diodes Incorporated type DFLS220L, ON Semiconductor type MBRA210LT3 and Philips type PMEG1020.

### INDUCTOR, L<sub>1</sub>

The LP55271 high switching frequency enables the use of the small surface mount inductor. A 4.7  $\mu\text{H}$  shielded inductor is suggested for 2 MHz switching frequency. The inductor should have a saturation current rating higher than the peak current it will experience during circuit operation (~1.7A at maximum load). Less than 300 m $\Omega$  ESR is suggested for high efficiency. Open core inductors cause flux linkage with circuit components and interfere with the normal operation of the circuit. This should be avoided. For high efficiency, choose an inductor with a high frequency core material such as ferrite to reduce the core losses. To minimize radiated noise, use a toroid, pot core or shielded core inductor. The inductor should be connected to the SW1 and SW2 pins as close to the  $I_{\rm C}$  as possible. Example of a suitable inductor is TDK type VLCF5020T-4R7N1R7-1.

**Table List of Recommended External Components**

| Symbol              | Symbol Explanation                                            | Value           | Unit | Туре                                         |

|---------------------|---------------------------------------------------------------|-----------------|------|----------------------------------------------|

| C <sub>VDD1</sub>   | V <sub>DD1</sub> Bypass Capacitor                             | 100             | nF   | Ceramic, X5R                                 |

| C <sub>VDD2</sub>   | V <sub>DD2</sub> Bypass Capacitor                             | 100             | nF   | Ceramic, X5R                                 |

| C <sub>OUT1,2</sub> | Output Capacitors from FB to GND                              | 2 x 10 µF ± 10% | μF   | Ceramic, X5R, 10V                            |

| C <sub>IN</sub>     | Input Capacitor from Battery Voltage to GND                   | 10 ± 10%        | μF   | Ceramic, X5R, 10V                            |

| C <sub>VDDIO</sub>  | V <sub>DD_IO</sub> Bypass Capacitor                           | 100             | nF   | Ceramic, X5R                                 |

| C <sub>VDDA</sub>   | V <sub>DDA</sub> Bypass Capacitor                             | 4.7             | μF   | Ceramic, X5R, 6.3V                           |

| C <sub>1,2</sub>    | Audio Input Capacitors                                        | 47              | nF   | Ceramic, X5R                                 |

| R <sub>T</sub>      | Oscillator Frequency Bias Resistor                            | 82              | kΩ   | 1%                                           |

| R <sub>F</sub>      | Flash Current Set Resistor for 370 mA Sink<br>Current         | 1300            | Ω    | 1%                                           |

| C <sub>VREF</sub>   | Reference Voltage Capacitor, between V <sub>REF</sub> and GND | 100             | nF   | Ceramic, X5R                                 |

| L <sub>1</sub>      | Boost Converter Inductor                                      | 4.7             | μН   | Shielded, low ESR,<br>I <sub>SAT</sub> ~1.7A |

| D <sub>1</sub>      | Rectifying Diode, V <sub>F</sub> @ maxload                    | 0.35            | V    | Schottky diode                               |

|                     | Flash LED                                                     | User defined    |      |                                              |

|                     | LED1 to LED4                                                  |                 |      |                                              |

|                     |                                                               |                 |      |                                              |

speed\_ctrl[2] en\_test en\_led4 boost[0] led1[0] led2[0] [0]Epa] led4[0] 8 0 0 0 0 speed\_ctrl[1] en\_led3 boost[1] led1[1] led2[1] led3[1] led4[1] 0 0 0 0 0 5 0 flashled\_ok en\_led2 en\_sync led1[2] freq\_sel boost[2] led2[2] led3[2] led4[2] **D**2 0 0 0 0 0 0 en\_autoload led4\_ok en\_agc en\_led1 led1[3] led2[3] led3[3] led4[3] boost[3] ľ **D**3 0 LP55271 Control Registers and Default Values threshold[0] dc\_freq en\_torch led3\_ok led1[4] led2[4] led3[4] led4[4] **D**4 2 0 0 0 threshold[1] gain\_sel[0] en\_flash en\_boost led2\_ok led1[5] led2[5] led3[5] led4[5] ١/٥ 02 0 0 0 0 0 0 threshold[2] flash\_sync gain\_sel[1] led1\_ok led1[6] led2[6] [9]Epə1 led4[6] nstby r/o 9**0** 0 0 0 0 0 0 0 safety\_time threshold[3] gain\_sel[2] led1[7] led2[7] led3[7] led4[7] 0 0 07 0 0 0 0 **Audio Sync Control2 LED Control Register Audio Sync Control1 LED Test Control Boost Output** REGISTER **ENABLES** LED3 LED2 LED4 LED1 r/o = Read Only ADDR (HEX) 8 0B 2B 00 0 **2A** 02 93 8 5

# Physical Dimensions inches (millimeters) unless otherwise noted

The dimension for X1, X2 and X3 are as given:

- $X1 = 2.466 \text{ mm} \pm 0.03 \text{ mm}$

- $X2 = 2.974 \text{ mm } \pm 0.03 \text{ mm}$

- $X3 = 0.60 \text{ mm} \pm 0.075 \text{ mm}$

## microSMD-30 **NS Package Number TLA3011A**

See National Semiconductor Application Note 1112 Micro SMD Wafer Level Chip Scale Package for PCB design and assembly instructions.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**Europe Customer Support Center**

**National Semiconductor**

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560